# IDEC Chip Design Contest

# A Low Power Voltage Step-up System for NAND Flash

School of Electrical Engineering, KAIST Hyun-Sik Jeong, and SeongHwan Cho

### Abstract

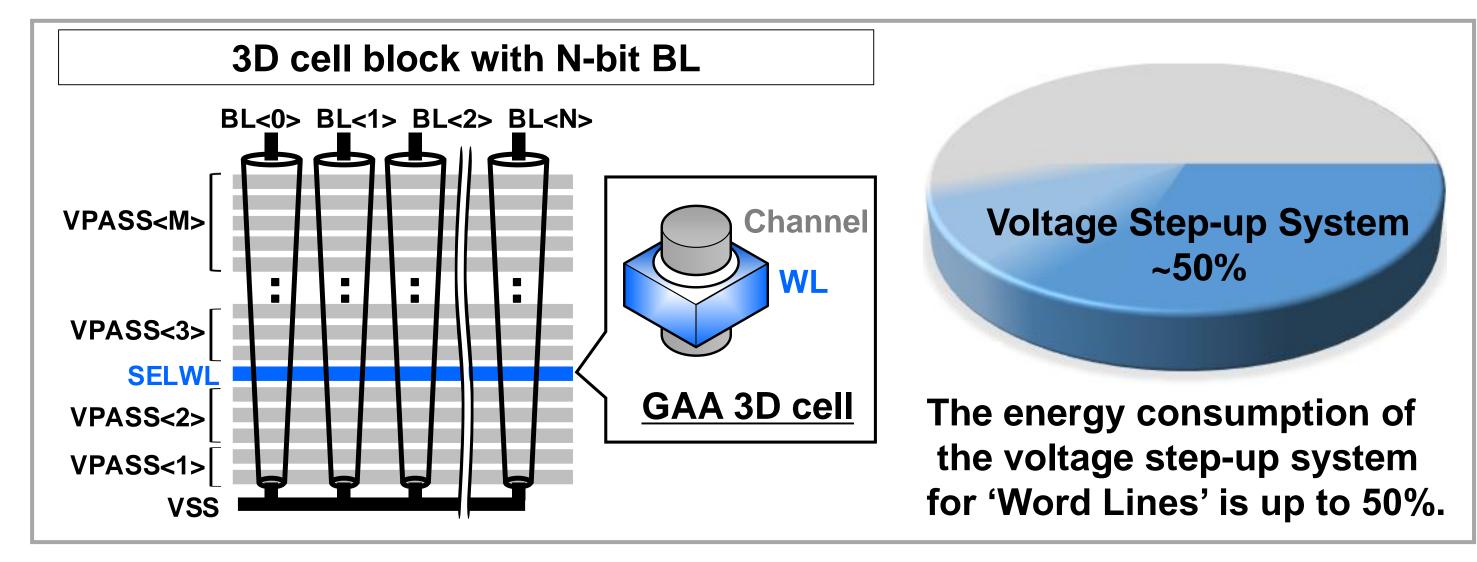

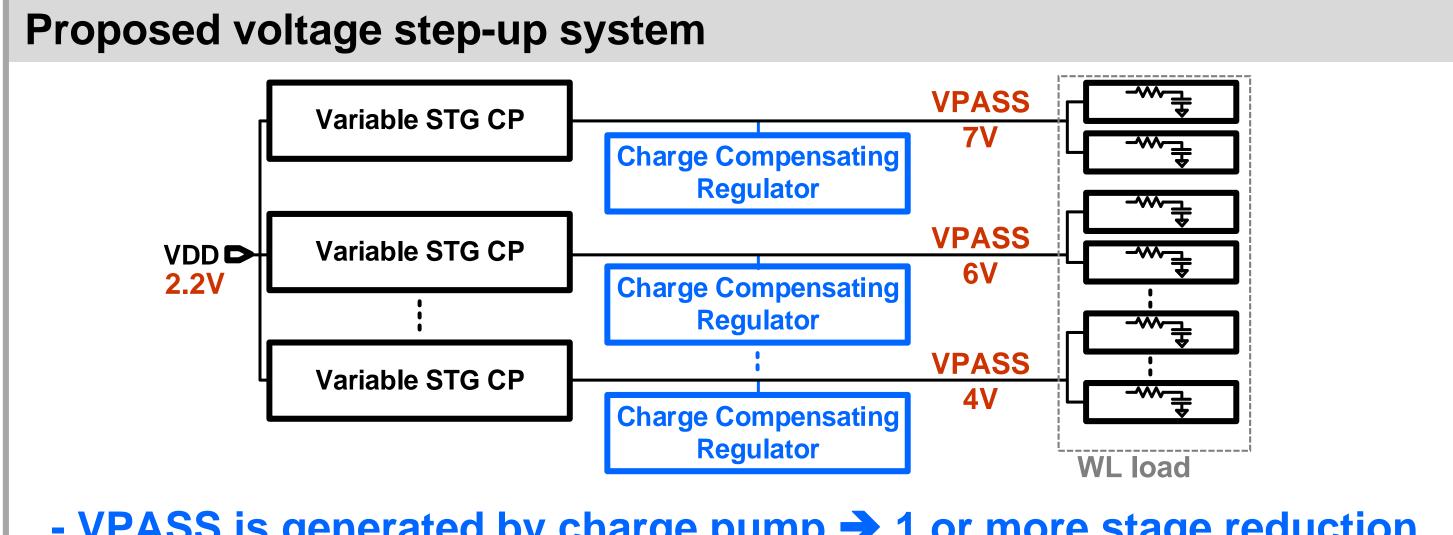

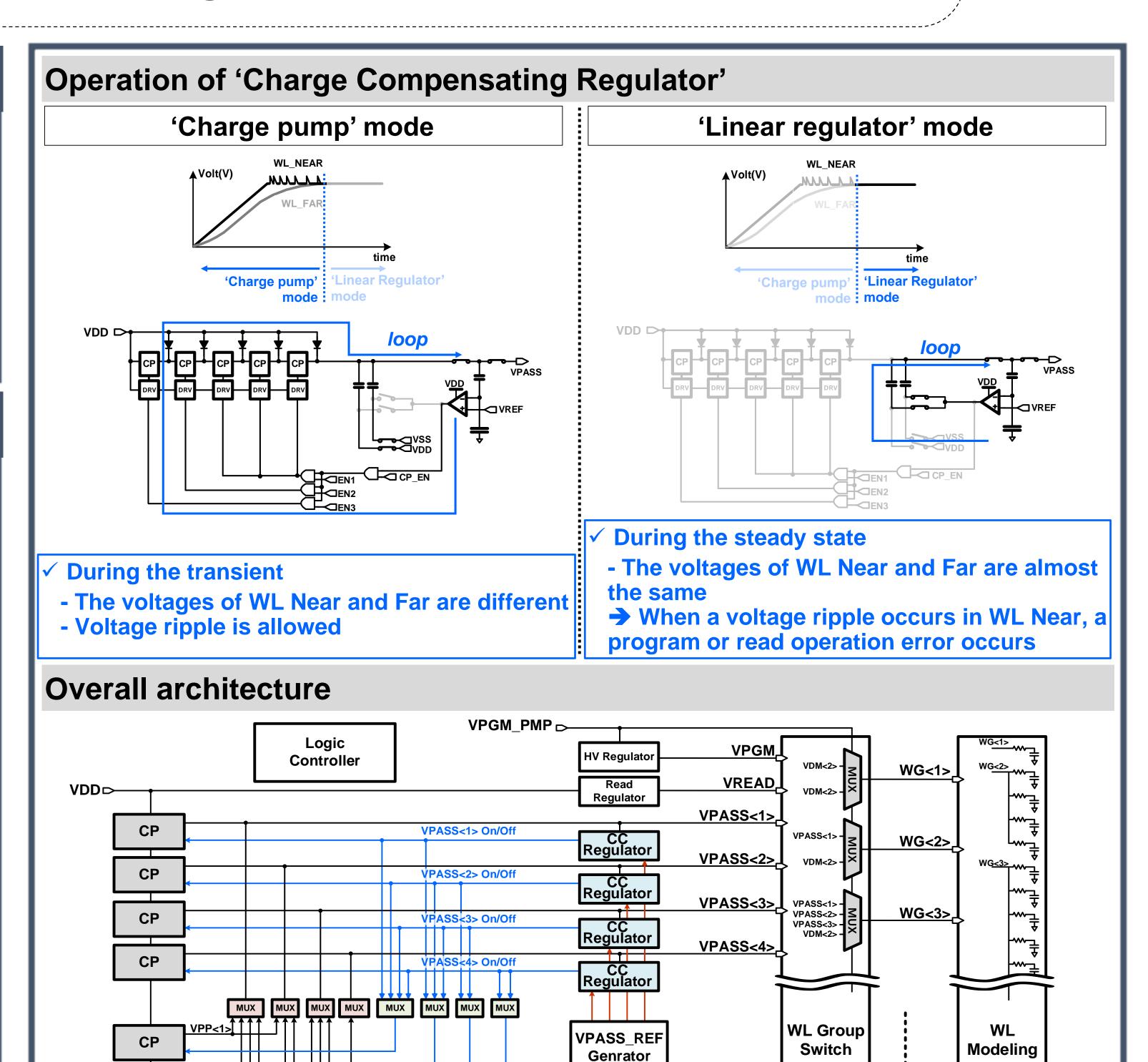

In order to reduce the energy of the voltage step-up system that uses up to 50% of the operating energy in 3D NAND flash, 'Variable stage charge pump system' and 'Charge compensating regulator' without voltage ripple during steady state were proposed.

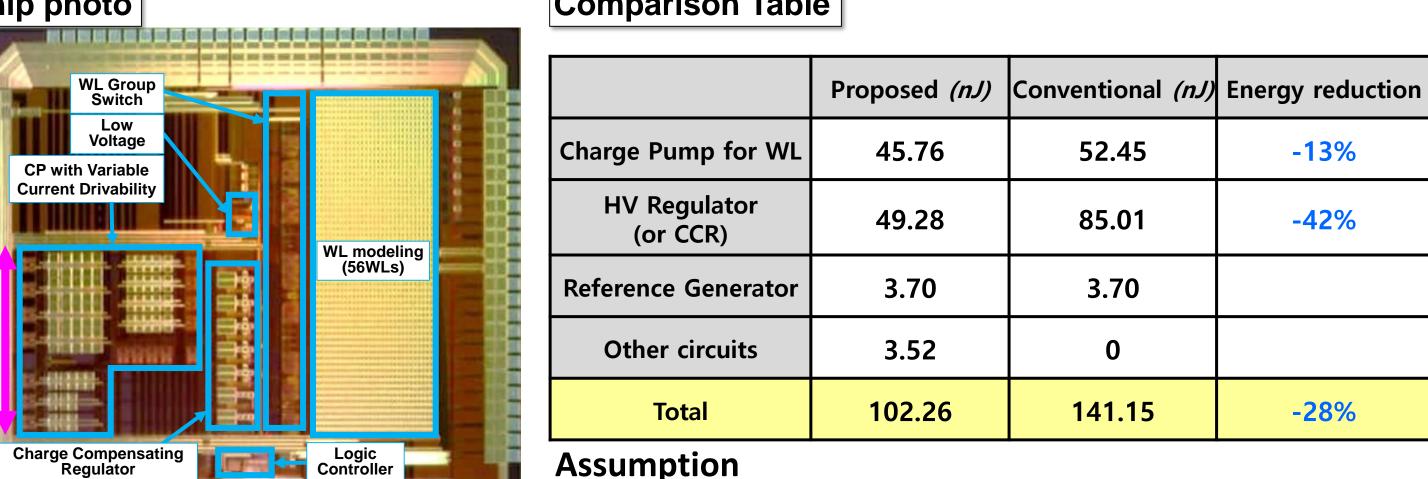

The chip fabrication for verification uses the Globalfoundaries 180nm UHV process, and a 56WL NAND flash system modeled with 10.1pF/WL (WL to GND), 3.0pF/WL (WL to adjacent WL), and 131kΩ/WL is constructed to create a traditional energy compared to the system was confirmed to improve by 28%.

#### Introduction

The cell density of NAND flash is improved by applying a Gate-All-Around 3D cell.

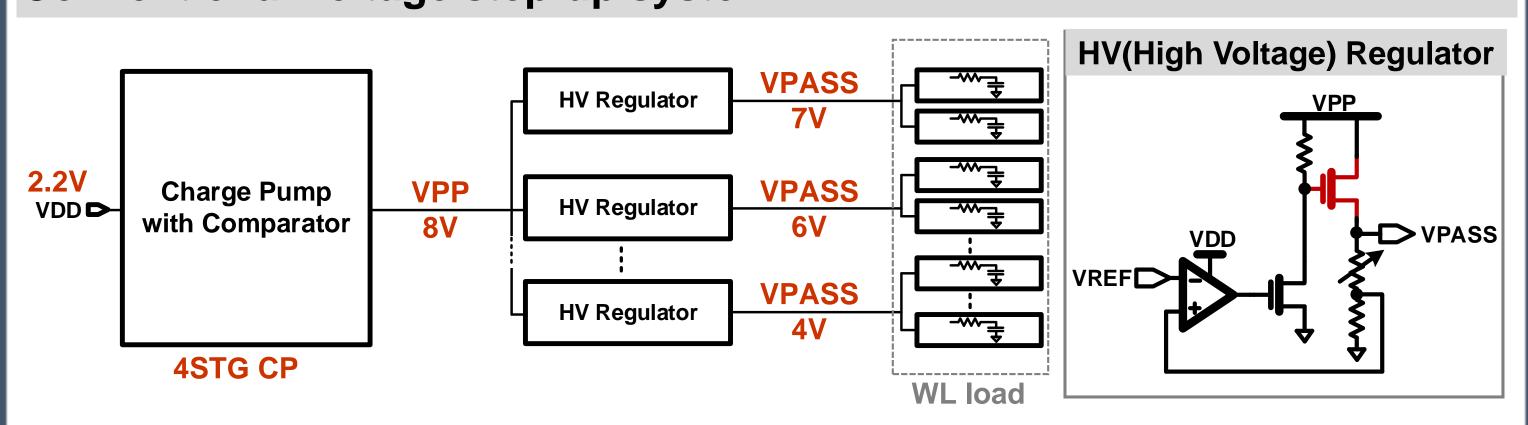

#### Conventional voltage step-up system

The regulator output uses NMOS. VPP must be sufficiently higher than the VPASS voltage.

**How to reduce** energy(or power) consumption?

## Proposed architecture & Implementation

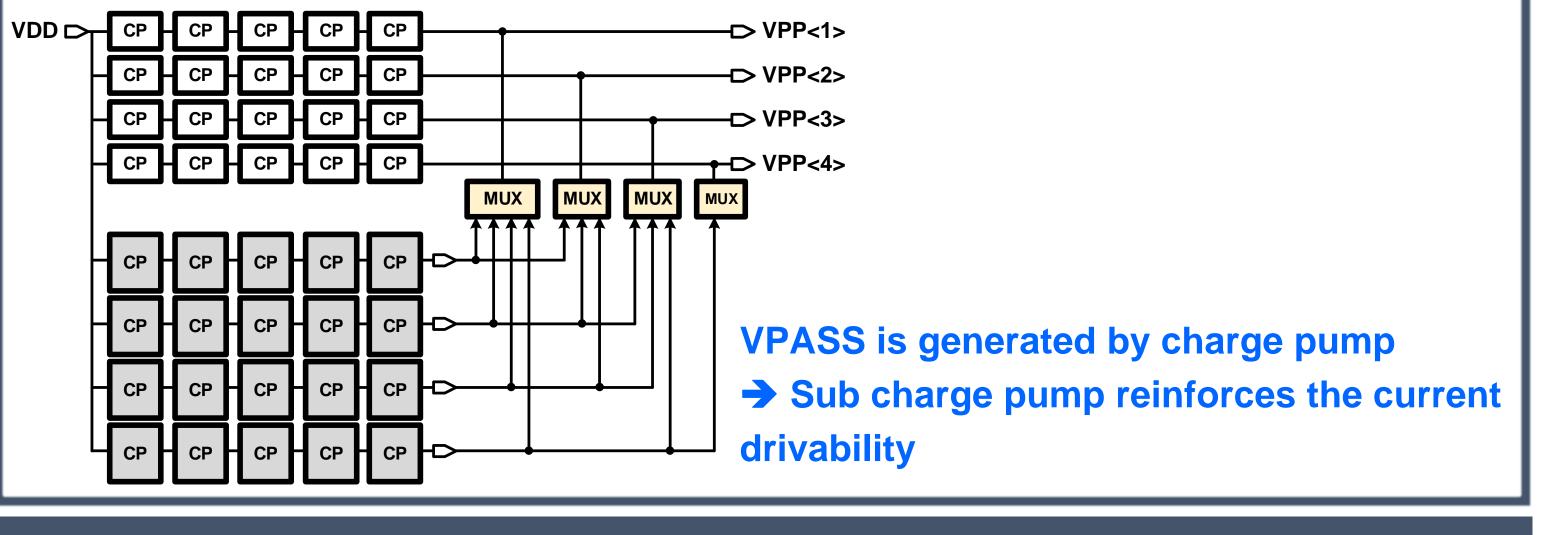

- VPASS is generated by charge pump -> 1 or more stage reduction

- CCR circuit suppressed voltage ripple.

#### Charge pump with variable stage and variable current drivability

### Acknowledgement

The chip fabrication and EDA tool were supported by the IC Design Education Center(IDEC), Korea.

Charge Compensating Regulator

CC Regulator

CC Regulator

VDM\_REF

**Charge Compensating Regulator**

**VDSL On/Off**

VDM<1> On/Off

**CP with Variable Current Drivability**

VPASS<2> - VPASS<4> - VDM<2> - X

**VDSL**

<u>VDM<1></u>

VDM<2>

WG<7>

WG<8>\_

WG<9>

WG<10>

#### Results Measurement results (WL Near) Simulation results PGM Pulse WL Eq. Verify WL Disch. **Voltage level of Cout's bottom plate Program operation plot WL Near & Far** Figured below CP Cout's bottom plate 520u 530u 540u 550u Bode plot @linear regulator mode Cain(dB) 20.0 -20.6 large WL small WL no ripple large WL by charge pumping Frequency(Hz) Chip photo **Comparison Table**

Quiescent current @HV Regulator: 5 uA/branch